## Digital Quad Integrating Photodiode with USB

#### **Features**

- simultaneous integration of up to 4 inputs at up to 1.1 kHz conversion rate

- gate time 6 µs to 1 s with internal timer

- gap-less **continuous** integration with gate times **500** µs to **1** s

- triggered measurements include signal and background acquisition

- 20 bit resolution

- ultra low noise:

**below shot noise** for many applications

- extreme dynamic range: up to 1:250 000

- high accuracy, low drift

- tunable full scale range 50 pC to 350 pC

- easy-to-use interface (USB, UART)

- external trigger rising or falling edge, TTL or LVDS

- Auxiliary ADC, DAC and GPIO pins

- small form factor: 60 x 40 x 22 mm<sup>3</sup>

- Affordable pricing

## **Applications**

- laser pulse monitoring and signal measurement in systems up to 1kHz

- digtial 2 or 4 segment photodiodes

- shot-to-shot pulse noise measurements

- continuous gap-free signal monitoring

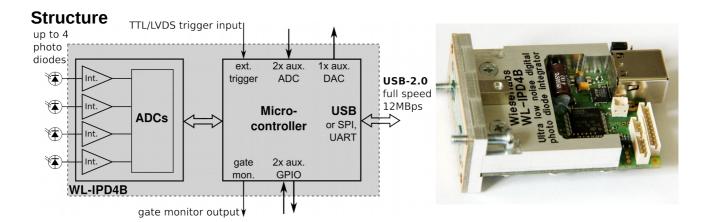

## **General Description**

The WL-IPD4B is a highly-integrated boxcar integrator to be attached directly to up to 4 photo diodes. After a trigger pulse, all 4 inputs are integrated simultaneously for an adjustable amount of time between 6 µs and 1 second (boxcar integrator). The measurement is digitized integrated 20 bit analog-to-digital usina converters with ultra low noise and exceptional dynamic range. Integration results are transferred over the USB link to a computer (alternatively: 3.3 V UART, SPI, I2C). In triggered mode, the IPD4B can continuously acquire 4 signal measurements and transfer them over the USB link at a trigger rate of up to 1.1 kHz. This allows shot-ot-shot measurements in systems with 1 kHz repetition rate. Internal triagering additionally allows gap-less boxcar integration mesurements with gate times 500 µs to 1 s e.g. for monitoring.

The USB interface registers itself as virtual serial port (VCP) for direct and easy integration into lab control software such as LabView. Communication uses a simple text-based protocol.

(Document Rev. 0.6a, 2015-08-28)

The information provided in this data sheet is believed to be accurate and reliable. However, Dipl.-Phys. Wolfgang Wieser assumes no responsibility for its use, for inaccuracies and omissions, nor for any infringements of patents or other rights of third parties that may result from its use. Prices and specifications are subject to change without notice. Trademarks and registered trademarks are the property of their respective owners.

# © Dipl.-Phys. Wolfgang Wieser www.wieserlabs.com

Agnes-Bernauer-Str. 96a, 80687 München, UStID: DE255278404

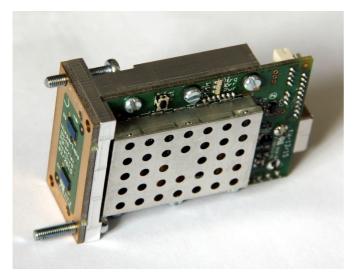

## **Photos**

Photos of the IPD4B. Different photo diodes can be mounted; the ones in the images are just examples.

The IPD4B can be modifed to have the photo diodes on the top and bottom instead of the front.

FIXME: Show connector.

## **Electrical Specifications**

| Parameter                        | Conditions               | Min | Тур | Max | Units |

|----------------------------------|--------------------------|-----|-----|-----|-------|

| Supply Voltage (V <sub>s</sub> ) |                          | 4   | 5   | 6   | V     |

| Supply Current                   | Normal operation (1 kHz) |     | 150 |     | mA    |

| TTL trigger input logic level    |                          | 3.3 |     | 5   | V     |

| Gate monitor output logic level  |                          |     | 3.3 |     | V     |

| LVDS trigger input               |                          |     |     |     |       |

|                                  |                          |     |     |     |       |

|                                  |                          |     |     |     |       |

|                                  |                          |     |     |     |       |

|                                  |                          |     |     |     |       |

|                                  |                          |     |     |     |       |

|                                  |                          |     |     |     |       |

|                                  |                          |     |     |     |       |

|                                  |                          |     |     |     |       |

|                                  |                          |     |     |     |       |

|                                  |                          |     |     |     |       |

|                                  |                          |     |     |     |       |

|                                  |                          |     |     |     |       |

|                                  |                          |     |     |     |       |

## **Mechanical Specifications**

| Size of board    | 54 x 40 | mm² |

|------------------|---------|-----|

| Weight (approx.) | ?       | g   |

#### **Photodiodes**

Photodiodes are attached in photo voltaic mode. The photo diodes are attached on a pluggable photo diode carrier board. This allows the use different photo diodes in different positions and with different distances. Contact us for custom placements and custom photo diodes.

## **Trigger Timing and Operation**

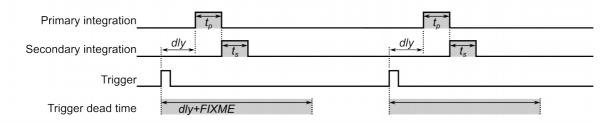

The IPD4B has 2 internal operation modes, **PS mode** and **CONT mode**.

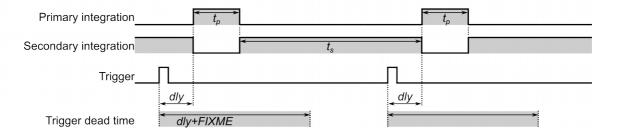

**PS mode** is the standard triggered integration mode. In PS mode, after a trigger event, the IPD4B performs two integrations and ADC conversions for each of the 4 input channels: First, a *primary* integration is performed with a gate time  $t_p$  between 6  $\mu$ s and 1 second as specified with the :time command (excluding the small range 351 to 364  $\mu$ s due to an internal limitation). The primary integration is reported as D:P: and is intended to be used to capture the photo diode signal of interest. For best results with a short pulsed laser source (pulse length much shorter than gate time), ensure that the laser pulse hits the photo diode at least 1  $\mu$ s after the start of the primary integration gate. Note that the true timing of the primary integration can be observed at GATE\_MON\_OUT (connector CON1, pin 1).

Immediately after the primary integration, a secondary ("background") integration is performed and then the IPD4B waits for the next trigger event without integrating the photodiode signal. The gate time  $t_s$  for the secondary integration is as long as the primary one for gate times up to 175  $\mu$ s and fixed at 10  $\mu$ s for larger gate times. It is recommended to set the trigger time and trigger delay such that the *primary* integration is the signal of interest. The secondary "background" result is usefully only in certain very rare circumstances: It is not a true background because it is acquired after and not during the primary integration. Especially, stray and unwanted ambient light which might be fluctuating with 100 or 120 Hz mains frequency cannot be properly captured and subtracted that way. Therefore, it is recommended to mechanically shield ambient light during the gate time instead of trying to subtract the secondary "background" result. Also subtracting the secondary measurement adds noise to the end result. Therefore, secondary integration results are not reported by default and must be activated using the subtraction.

**CONT mode** allows <u>continuous gap-free integration</u> and can be activated for gate times  $t_p$  of 400  $\mu$ s and larger. In CONT mode, *primary* and *secondary* integrations (reported as D:P: and D:S:, respectively) are alternating and both results need to be used to obtain gap-free signal coverage. CONT mode also requires a periodic trigger but in most applications, the internal periodic trigger is easiest to use. After a trigger event, the IPD4B completes the running secondary integration and immediately starts a primary integration with a gate time of  $t_p$  as specified with the :time command. After the gate time, it starts a secondary integration which runs until the next trigger event. Hence,  $t_p + t_p$  is the trigger repetition time. Note: Since secondary integration results are not reported by default, they must be activated using the :rmask command.

Example: For continuous gap-less integration of all 4 photo diodes, set the internal trigger mode to "periodic" and the gate time to half the trigger period. Let's assume we want integration results at a rate of 500 Hz. So, we set the internal periodic trigger to a 2000  $\mu$ s interval time (i.e. 500 Hz rate) and use a 1000  $\mu$ s gate time:

```

:itm per

:itp 2000 1

:dly 0

:rmask 0xff

:t 1000

```

Offset subtraction. The IPD4B has an intrinsic signal offset. Even if all photo diodes are in complete

darkness or no photo diodes are attached at all, a certain small signal is reported. This is typically about 0.4% full scale (reported value about 4000). This offset is intentially present to allow measurements in presence of small leakage currents. Otherwise, with a hard clipping at zero, leakage currents through the photo diode would introduce an offset error in the integration results. It is recommended to measure an average offset without light on the photo diodes for every channel over several trigger events. This average offset can then be subtracted from the reported integration results. Please note that due to leakage currents, the offset varies slightly with integration time, so for optimum result is is recommended to measure the offset at the same gate time as later the integration results. Also, when using primary and secondary integration results, the offset has to be measured for primary and secondary gates independently.

**Trigger dead time.** If a trigger event occurs during the trigger dead time, it is ignored. It is not recommended to trigger during the trigger dead time as this can increase the noise.

## PS mode

#### **CONT** mode

**Internal result buffer:** The IPD4B has an internal queue which is capable of storing up to 1024 results. This makes it easier to keep up with the conversion rate using PC software receiving data from the USB link. If the result buffer runs full, the IPD4B starts to discard the oldest results in the queue and overwrites them with new ones. If results are lost, this is reported in the result string using an "L" at the end (see response format).

#### **Noise Performance**

FIXME.

#### **USB VCP Interface**

The USB interface is a USB-1.1 full speed (12 Mbps) link applying an FTDI USB-to-serial converter. With the appropriate Windows-drivers from <a href="https://www.ftdichip.com">www.ftdichip.com</a>, the USB link presents itself as a virtual

COM port (VCP) on the host computer. On Windows 7, the drivers install themselves automatically via Winows Update. Linux VCP drivers are part of every recent Linux kernel (module ftdi sio).

The VCP has to be initialized for 1000 kbaud (divisor 24), raw transmission, no echo, 8 bit, no parity, 1 stop bit ("8n1") and RTS/CTS hardware flow control. The corresponding initialization commands unter Linux are:

```

stty -F /dev/ttyUSB0 38400 raw pass8 -echo crtscts setserial /dev/ttyUSB0 spd cust divisor 24

```

In LabView (Windows), simply use VISA serial open and initialize the associated COM port to 1 000 000 baud, 1 stop bit, no parity bit, RTS/CTS flow control. Example LabView software is provided.

## **USB Data and Response Format**

The IPD4B by default transmits data in an ASCII line-based human readable (non-binary) format. Lines are terminated by a CR/LF combination. Commands sent to the IPD4B are to be sent in CR (or CR/LF) terminated ASCII text strings. Typical messages received from the IPD4B look as follows:

```

R: cmd=5 err=0

D:P: 60720 60944 66832 66256 37373632

D:P: 61367 61232 66902 66112 37348632

```

Each line starts with a type field (start of line, e.g. "R:" or "D:P:").

List of types:

| Type field                                                    | Description                                   |  |

|---------------------------------------------------------------|-----------------------------------------------|--|

| R: "response": Command response (from response queue)         |                                               |  |

| D:P: "data": Primary integration result (from result queue)   |                                               |  |

| D:S: "data": Secondary integration result (from result queue) |                                               |  |

| MSG:                                                          | "message": Result message (from result queue) |  |

**Command response:** "R:" denotes command responses. An "R" line is generated for most commands sent to the IPD4B.

```

R: cmd=5 err=0

```

The figure after "cmd=" (here: 5) is the internal command name. The figure after "err=" (here: 0) denotes the error code. Code 0 is always "success" (no error). List of error codes:

| Error code                     | Description                           |  |

|--------------------------------|---------------------------------------|--|

| 0                              | Success (no error)                    |  |

| 1                              | 1 Argument out of range               |  |

| 2 Missing argument for command |                                       |  |

| Too many arguments for command |                                       |  |

| 4                              | Wrong number of arguments for command |  |

| 5                              | Unknown command                       |  |

| 6                              | Argument format error                 |  |

Integration results: Lines starting with "D:" contain integration ADC results ("data"). There are 2

different types of ADC results: Primary and secondary, "D:P" and "D:S", respectively. Secondary integration results (e.g. "background") are disabled by default and need to be enabled using command :rmask.

```

D:P: 60720 60944 66832 66256 37373632

D:S: 60720 60944 66832 66256 37373632 L

```

The first 4 figures are the 4 ADC conversion results for the 4 photo diode channels. Data range is 0 to 2^20-1 (1048576). All further figures must be ignored. If results were dropped due to result queue overflow, then an "L" at the end of the line indicates this (see second line above).

**Result message:** Lines starting with "MSG:" are messages queued in the same queue as the integration results. The reason for keeping them separate from the comand responses ("R:") is that these messages indicate status related to the integration and therefore need to be queued in the same queue as the integration results so that the relationship between the message and the previous and next integration result is kept intact.

```

MSG: 2 1 1308 37373632

```

The fields are: message code (here: 2), status code (here: 1), status detail (here: 1308). All further figures must be ignored (reserved for future expansioon). If results were dropped due to result queue overflow, then an "L" at the end of the line indicates this just as with the integration results above. List of message codes:

| Message code | Description                                                                                                                                                                                                                                                          |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0            | No message (should never happen)                                                                                                                                                                                                                                     |

| 1            | Reconfig: This is generated in the result queue after a re-config has occured. All results before this message were taken with the old parameter set and all results after this message were generated with the new parameter set. The status code is 0 for success. |

| 2            | <b>Timeout:</b> Internal state machine timeout. The status code indicates the number of pending results.                                                                                                                                                             |

The status detail indicates the source code position where the message was generated. It can change during firmware updates and is not intended for any use besides communication with the vendor.

#### **USB Commands**

The IPD4B can be configured by sending commands over the USB link. The command format is ASCII text terminated by CR (or CR/LF). The command structure is always:

```

:cmd [arg1] [arg2] [...]

```

The first character is a ':' denoting a command start.

cmd is one of the command strings listed below.

arg1, arg2 are optional arguments for the command.

Commands can be sent to the IPD4B while integrations are in progess. Most commands do not directy affect the active properties of the IPD4B but are stored in shadow registers. This new configuration in the shadow registers has to be explicitly activated by a re-configuration command (reconfig, stop, cont) is set. Most commands are acknowledged using an R: response. Note that the IPD4B has an internal response queue (which is separate from the result queue) and can hold up to 16 responses. Therefore, one can send several commands and then receive several responses.

**NOTE:** The USB virtual COM port interface is typically not in interactive mode, i.e. it will not echo back characters typed in and will not honor backspace. In order to enter interactive mode, send "i" followed by a CR/LF. In order to leave interactive mode, send "i 0" followed by CR/LF. These commands do not have a colon ":" at the beginning. **NOTE:** Interactive mode is only recommended for terminal emulation with human character entry and not for automated control e.g. from LabView or other software.

Set the integration time to NNN  $\mu$ s. If a "c" is specified as second argument, the IPD4B is in CONT mode, otherwise it is in standard PS mode.

PS mode: Valid gate time range is 6 to 1000000 µs excluding 351 to 364 µs.

CONT mode: Valid gate time range is 400 to 1000000 µs.

Requires re-config to take effect.

Set trigger delay in  $\mu$ s. Valid range is 0 to 100s (100000000 $\mu$ s). An external or internal trigger will be delayed by this time before the triggered integration begins. Note that delays may not overlap the next trigger, so for a delay of D and an integration time of N, the device will ignore all triggers for time D+N. The highest trigger repetition rate is 1.x kHz.

Requires re-config to take effect.

#### :etp r|f

Set external trigger polarity to rising ('r') or falling ('f') edge triggered.

#### :rmask NUM

Set the result mask. Not all results are queued in the result queue to save bandwidth and queue space. The result mask is a bitmask which selects the results to be stored and transferred. It can be specified in hexadecimal (e.g. 0x12) or decimal (e.g. 18) notation.

Currently the following result types are defined:

| Result<br>Type | Type<br>field | rmask<br>value | Description                        |

|----------------|---------------|----------------|------------------------------------|

| 1              | D:P:          | 0x02           | Primary integration results.       |

| 2              | D:S:          | 0x04           | Secondary integration results.     |

| 3              | D:A:          | 0x08           | Auxiliary IO (not yet implemented) |

| 4              | MSG:          | 0x10           | Messages                           |

The rmask value corresponds to the n-th bit where n is the result type, i.e. (1 << result\_type). For instance, to select results from primary integration and messages, set rmask to 0x12.

Acts immediately; does not require a re-config to take effect.

#### :itm off|per|dly

Set internal trigger mode:

- off no internal trigger; use external (LVDS/TTL) trigger

- per periodic internal trigger; this can be used to periodically start an integration without external trigger

- dly use the internal trigger timer to provide an extended external trigger delay. This allows to realize delays which are longer than the trigger period of the external trigger. This is extremely useful for implementing a slightly "negative" trigger delay on a repetetive trigger.

Example: A Ti:Sa laser is operated at 1 kHz and generates a trigger at 1 kHz. An integration time of 20  $\mu$ s is chosen. Due to the intrinsic delay in the IPD4B and the time spent in cables and optics, the optimum trigger delay might be -15  $\mu$ s or +985  $\mu$ s. If 985  $\mu$ s is set via :dly, then only every second trigger will be accepted due to the dead time. Solution: Set the internal trigger to delay mode with a 500  $\mu$ s delay and do the remaining 485  $\mu$ s using the regular trigger delay:

```

:itm dly

:itp 500 1

:dly 485

```

Requires re-config to take effect.

```

:itp PER [PSC]

```

Internal trigger period and prescaler. This is only relveant for internal trigger modes "dly" and "per". Valid range is 0 to 65535 for PER and 1 to 4000 for the prescaler. The final internal trigger time is PER \* PSC in  $\mu$ s. If the internal trigger is in "per" mode (period), this specifies the rate at which an internal trigger signal is generated. For "dly" (delay) mode, this specifies the extended trigger delay time.

Requires re-config to take effect.

```

:rc

:reconfig

```

Re-configure; this is required so that the settings made with various commands (time, trigger delay,..) takes effect.

```

:s

:stop

:c

:cont

```

Stop the integrator and continue again. Stop is essencially a re-configuration with all triggers disabled.

#### :reset

Complete reset of the IPD4B device; will re-boot the firmware. This removes all results and resets all settings to power-on defaults. This is useful to enter the bootloader for firmware update. It is not used during typical normal operation.

#### :version

Write the firmware version string.

#### :test

Enter integrator test mode. In this mode, the photo diodes are detached from the integrator and ADC and the observed noise is only due to the ADC and electronics.

#### :istat NNN

Mainly for testing. If NNN>0, statistics for the primary and secondary integration on each channel are emitted for every NNN results (1 to 10000):

| STAT:P: | 3891 | 3814 | 4038 | 4106 | 4.7 | 5.9 | 5.6 | 6.0 |

|---------|------|------|------|------|-----|-----|-----|-----|

| STAT:S: | 3516 | 3519 | 3731 | 3709 | 5.5 | 6.5 | 5.8 | 6.4 |

The first 4 figures are the average and the second 4 figures the standard deviation with 1 digit of precision.

A typical example would be to configure the integration for 500µs rising edge triggered with no delay. Note that there is always an intrinsic delay from the trigger to the start of the integration FIXME: How large? The actual integration window after the trigger can be observed at the TRIG\_MON trigger monitor pin.

:t 500

:dly 0

:etp r

:reconfig

## **Electrical Interfacing**

Supply voltage: 4.5-9V (external or via USB).

Current consumption: 130mA typical

Trigger interface: 3.3V to 5V digital input for TTL input and usual LVDS levels for LVDS input.

Gate output: 3.3V digital output which is HIGH as long as the primary integration gate is active.

#### On-board LEDs:

- · green power LED: always on if power is present

- red status LED: TBD

- green status LED: blinking to indicate IPD4B is alive and operational; fast blink frequency during boot load process

- green USB indicator LED (near USB connector): indicates data going over the USB (both directions)

**NOTE:** A lot of optional functionality (auxiliary ADC, DAC, GPIO, interfacing via UART, SPI) is physically present on the design but needs a suitable firmware to be usable. **Contact us if you would like to use this functionality.**

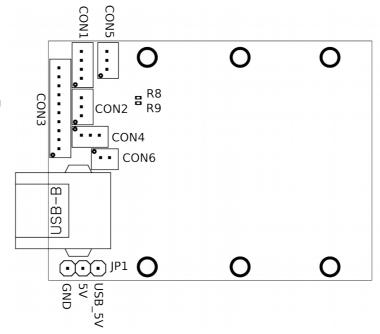

## **Connector Pinouts**

External TTL trigger input and integration gate monitor output (CON1):

| Pin | Name         | Description                                                                                                                                                                                               |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GATE_MON_OUT | Gate monitor output (3.3V).                                                                                                                                                                               |

| 2   | GND          | Ground connection.                                                                                                                                                                                        |

| 3   | TRIG_IN      | Trigger input (3.3V or 5V) if CMOS/TTL trigger source is implemented. To select the CMOS/TTL trigger input, resistor <b>R8</b> needs to be inserted (100 Ohm) and resistor <b>R9</b> needs to be removed. |

| 4   | GND          | Ground connection.                                                                                                                                                                                        |

## External LVDS trigger connector (CON2):

| Pin | Name          | Description                                                                                                                                                                                                                                                                               |

|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | LVDS_TRIG_IN+ | Positive LVDS line for external trigger input. Only avaliable if LVDS input is configured. To select the LVDS trigger input, resistor <b>R9</b> needs to be inserted (100 Ohm) and resistor <b>R8</b> needs to be removed. LVDS termination can be inserted via R20 (100 Ohm) if desired. |

| 2   | LVDS_TRIG_IN- | Negative LVDS line for external trigger input. Only avaliable if LVDS input is configured. See pin 1.                                                                                                                                                                                     |

| 3   | GND           | Ground connection.                                                                                                                                                                                                                                                                        |

## Communication connector (optional) (CON3):

| Pin | Name        | Description                                                                                                                                            |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   |             | Unused (RFU)                                                                                                                                           |

| 2   | 3.3V        | 3.3V supply from the integrator board. Can be used as IO voltage reference for attached logic. Max power drawn: 20mA                                   |

| 3   | MOSI        | SPI MOSI (3.3V level) if SPI interface is implemented in firmware.                                                                                     |

| 4   | MISO<br>RTS | SPI MISO (3.3V level) if SPI interface is implemented in firmware.<br>Serial RTS (3.3V level) if serial interface is implemented in firmware.          |

| 5   | SCK<br>CTS  | SPI SCK (3.3V level) clock if SPI interface is implemented in firmware.<br>Serial CTS (3.3V level) if serial interface is implemented in firmware.     |

| 6   | GND         | Ground connection.                                                                                                                                     |

| 7   | NSS         | SPI NSS slave select (3.3V level) if SPI interface is implemented in firmware.                                                                         |

| 8   | SDA<br>RXD  | SDA serial data if I2C interface is implemented in firmware. (3.3V level)<br>Receive data if serial interface is implemented in firmware. (3.3V level) |

| 9   | SCL<br>TXD  | SCL serial clock if I2C interface is implemented in firmware. (3.3V level) Transmit data if serial interface is implemented in firmware. (3.3V level)  |

| 10  | GND         | Ground connection.                                                                                                                                     |

## Auxiliary GPIO (general purpose digital input/output) connector (optional) (CON4):

| Pin | Name | Description        |

|-----|------|--------------------|

| 1   | GND  | Ground connection. |

| 2 | GPIO1 | Auxiliary GPIO pin (3.3V level); must be activated in firmware. |

|---|-------|-----------------------------------------------------------------|

| 3 | GPIO0 | Auxiliary GPIO pin (3.3V level); must be activated in firmware. |

## Auxiliary ADC connector (optional) (CON5):

| Pin | Name        | Description                                           |

|-----|-------------|-------------------------------------------------------|

| 1   | AUX_ADC_IN1 | Auxiliary ADC input 1; must be activated in firmware. |

| 2   | AUX_ADC_IN0 | Auxiliary ADC input 0; must be activated in firmware. |

| 3   | GND         | Ground connection.                                    |

## Auxiliary DAC output (optional) (CON6):

| Pin | Name        | Description                                                                                                           |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------|

| 1   | AUX_DAC_OUT | Auxiliary DAC output. The auxiliary DAC is present on the microcontroller an can be activated with suitable firmware. |

| 2   | GND         | Ground connection.                                                                                                    |

## Supply pin header / jumper (JP1):

| Pin | Name   | Description                                                                                                                                                                       |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | USB_5V | 5V from the USB output.                                                                                                                                                           |

| 2   | 5V     | 5V supply input for the IPD4B. For USB powered operation, connect pins 1 and 2 with a jumper. For external power supply, connect power between pins 2 and 3 and leave pin 1 open. |

| 3   | GND    | Ground connection.                                                                                                                                                                |

The supply pin header is a standard 2.54 mm pin header. All other connectors mentioned above mate with ZHR-*n* (*n* being the number of pins) from JST, available e.g. at DigiKey.

The image on the right shows the location of the electrical connections. Pin 1 is marked.